Description

Used in over 600 million devices, HDMI represents the most common interconnect standard for high definition video and audio.

The Bitec HDMI 2.0b IP Core enables HDMI interconnectivity in FPGA or ASIC devices. Supporting pixel clocks to 600Mhz, the IP core allows ULTRA HD designs while using minimal device i/o pin resources. The core can operate in 1-, 2- or 4-symbols per clock allowing for high pixel rates on low end device technologies.

Both Video and Audio is supported with added low-level access to Auxiliary data packets. This feature allows low level development and testing of HDMI interfaces. It also allows a more flexible interface to the latest 3D and 4K video formats and control packets.

The core provides convenient interfacing to 3rd party SERDES for rapid development of image processing systems. It is also designed to operate in parallel with the Bitec DP 1.2 IP Core to achieve DP++ compatibility.

The IP Core has been interoperability tested at various CEA HDMI Plugfest events and is fully Certified.

Receiver Features

- HDMI 2.0b and 1.4a Compatible

- 8,10,12 & 16 bit Deep-color support

- 1-, 2- or 4-symbol/pixel per clock input/output

- Supports RGB, YCbCr Colorimetric Formats

- 2-, 8 and 32-channel Audio support

- 3D and MST Audio support

- Raw auxiliary data stream output

- Seamless interface to device transceiver

- Compatible with DVI and Dual-Link DVI Standards

- Optional CEC 1.4 and 2.0 support

- Optional HDCP 1.4/2.3 support

- ASIC Version available

Transmitter Features

- HDMI 2.0b and 1.4a Compatible

- 8,10,12 & 16 bit Deep-color support

- 1-, 2- or 4-symbol/pixel per clock input/output

- Supports RGB, YCbCr Colorimetric Formats

- 2-, 8 and 32-channel Audio support

- 3D and MST Audio support

- Raw auxiliary data stream input

- Seamless interface to device transceiver

- Compatible with DVI and Dual-Link DVI Standards

- Optional CEC 1.4 and 2.0 support

- Optional HDCP 1.4/2.3 support

- ASIC Version available

Technology Support : MicroSemi PolarFire, Lattice ECP5, Altera GX devices, ASIC

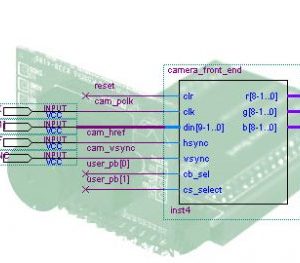

The HDMI core supports both sink and source. The sink video, audio and auxiliary data ports are designed to allow direct pass through of the HDMI data.

The core can operate in either 1-, 2- or 4-symbol/pixel per clock allowing low cost devices to handle video pixel clocks up to 600Mhz (UHD). The core interfaces directly to the FPGA device transceiver input and outputs. With a rich set of parameterizations, the core can be balanced for feature support and device utilisation.

When used in parallel with the Bitec DP 1.2 IP core, DP++ based designs are achieved.DP++ allows a single DP 1.2 interface connector to support both DP and HDMI connectivity.

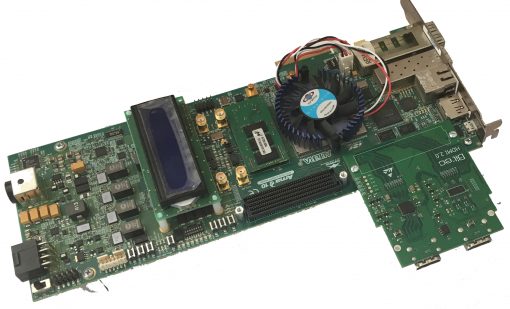

Intel Arria 10 FPGA Evaluation Platform

Evaluation platforms are available based on the Bitec HDMI Daughter card or Bitec FMC HDMI Daughter card. Reference designs are available which demonstrate the loop-through of video from source to sink on Intel Arria 10 FPGA development kits. Other device development kits are also supported. The example designs loop through source to sink up to 4K60 with optional HDCP 1.4 and HDCP 2.2 support.

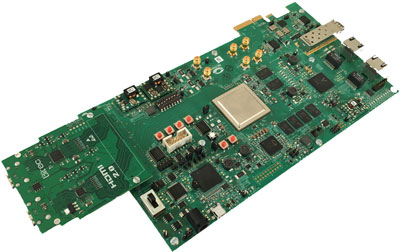

Microsemi PolarFire FPGA Evaluation Platform

The Microsemi FPGA Evaluation platform is available using the Bitec FMC HDMI Daughter card. Reference designs are available which demonstrate the loop-through of video from source to sink up to 4K60 with optional HDCP 1.4 and HDCP 2.2 support.

Optional HDCP

An optional HDCP encryption and decryption feature is available using the Bitec HDCP IP Core. The HDCP feature enables designs to operate with consumer and pro-AV equipment which need to transfer copyright video material.