Description

DisplayPort heralds a new alternative in video connectivity. Designed to enable low cost direct drive monitors and backed by industry leaders (Intel, DELL, Apple etc) DisplayPort is not hindered by license and royalty fees.

The Bitec DisplayPort IP core enables DTV manufacturers to rapidly develop and deliver displays offering a superior viewing experience within ever-shrinking product lifecycles.

The Bitec DisplayPort IP core accepts 1,2 or 4 lanes at either 1.62, 2.7, 5.4 or 8.1 Gbps link rate (includes eDP additional rates), in compliance with the DisplayPort 1.4 specification.

Receiver Features

- DisplayPort 1.4a compatible (includes eDP 1.4)

- eDP compatible

- Support for 1,2, 3 & 4-lanes

- Support arbitrary link rates (includes eDP rates)

- Support 8K60 YCbCr4:2:0 resolution

- HDCP 1.3/2.2 (optional)

- 6,8,10,12 & 16 bit color support

- Supports RGB, YCbCr Colorimetric Formats

- MCU (Portable C API) managed or autonomous AUX channel

- AUX Channel messages to 256-byte

- AUX debug channel

- User selectable AUX register SoPC Interface

- SoPC Integration

- Clock Recovery support

- DP 1.4a Multi-Stream support

- FreeSync support

- Global Time Code (GTC)

- 8-Channel Audio Support

- Forward Error Correction (FEC)

- Display Stream Compression 1.2a (DSC) (optional)

- Test Automation for Compliance Testing

- ASIC Version available

- ALPM Support

- Power optimized architecture via clock management

- Fully VESA Certified

Transmitter Features

- DisplayPort 1.4a compatible (includes eDP 1.4)

- Support for 1,2,3 & 4-lanes

- Support 1.62, 2.7, 5.4 and 8.1 Gbps link rate (includes eDP rates)

- Support 8K60 YCbCr4:2:0 resolution

- HDCP 1.3/2.2 (optional)

- 6,8,10,12 & 16 bit color support

- Supports RGB, YCbCr Colorimetric Formats

- MCU managed AUX channel

- AUX Channel messages to 256-byte

- AUX debug channel

- User selectable AUX register SoPC Interface

- SoPC Integration

- DP++ (DVI/HDMI) compatible

- DP 1.4a Multi-Stream support

- FreeSync support

- LTTPR support

- Global Time Code (GTC)

- 8-Channel Audio Support

- Forward Error Correction (FEC)

- Display Stream Compression 1.2a (DSC) (optional)

- Test Automation for Compliance Testing

- ALPM Support

- Power optimized architecture via clock management

- Fully VESA Certified

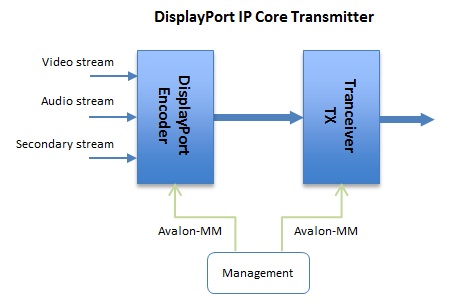

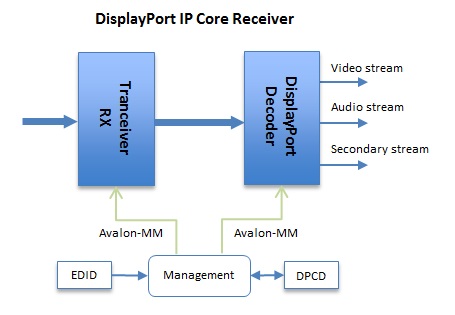

Video data is input to the core Transmitter as parallel data with H-sync, V-sync and Data Enable signals. Audio and secondary data streams are also supported and available for transport.

The core Receiver can output received video data on a stream interface for convenient interfacing to downstream logic. Audio and all Secondary Data are available in parallel format on their respective outputs. Both Receiver and Transmitter can use optional AUX debug ports for run-time AUX message log and monitoring.

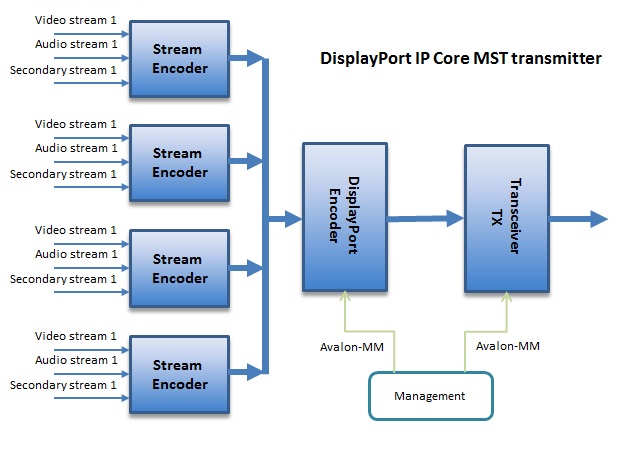

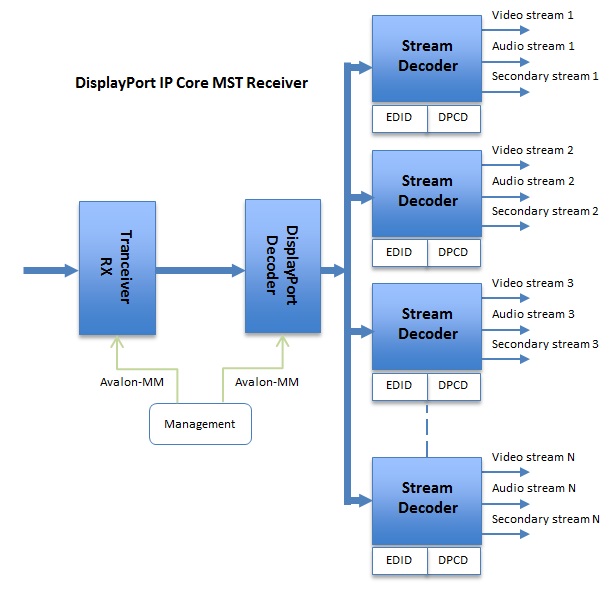

Multi-Stream (MST) applications

The Bitec DisplayPort IP Core Receiver supports Multi-Stream, a powerful DisplayPort v.1.4a feature allowing to transfer video and audio content for more than one display using only a single cable. For instance, four Full-HD streams (1920 x 1080p @ 60 Hz) can be delivered to the Receiver using Multi-Stream or a single 4K@60 stream (3840 x 2160 @ 60 Hz) using either Multi- or Single-Stream mode.

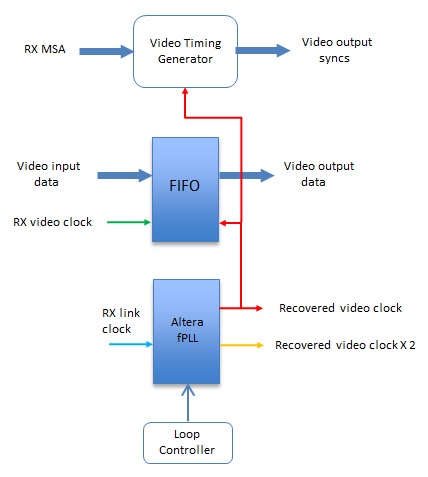

Clock Recovery support

A Clock Recovery block is available for the Bitec DisplayPort IP Core Receiver when the application requires DisplayPort received video data to be output together with the synthesized original pixel clock. This feature is useful, for instance, for outputting HDMI and analog video without using a frame buffer. The clock recovery feature is licensed separately.

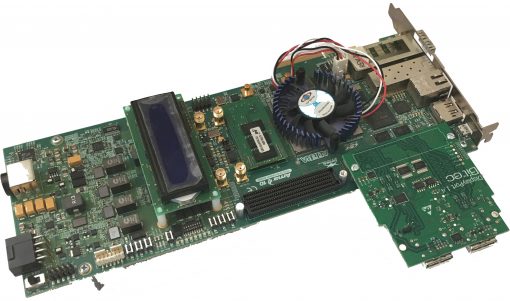

Intel Arria 10 GX DisplayPort Evaluation kit

An evaluation kit is available to allow application development using the Bitec DisplayPort IP Core. The kit includes an Arria 10 GX development kit (Stratix V available on request), a Bitec DisplayPort FMC daughtercard and a DisplayPort cable. An Opencore evaluation Bitec DisplayPort IP Core is requried. The Opencore evaluation gives full functionality of the core under the standard Opencore terms. The Bitec DisplayPort Daughter Card allows easy interfacing to standard source and sink devices . Bitec also offer a tailoring service for bespoke designs. Contact Bitec for more details.

Various reference designs are available which demonstrate

- Full DP 1.4a functionality

- Link rates to 8.1Gbps

- Multistream Video Receiver and Transmitter

- 8K@30 loopthrough

- Pixel Clock recovery

- DP++ using the Bitec HDMI IP Core

- Display Stream Compression (Upon request)

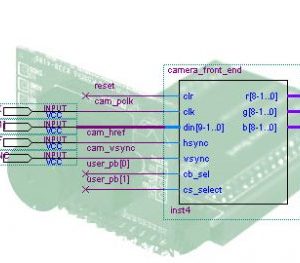

Lattice DisplayPort Development Boards

Lattice’s DisplayPort input and output boards are available for low-power, production-priced ECP5 FPGAs. These boards are part of the Video Interface Platform (VIP) ecosystem. These boards add the DisplayPort interface to Lattice’s award-winning Embedded Vision Development Kit (EVD Kit) using Bitec’s IP. Bitec also offers a tailoring service for bespoke designs. Contact Bitec for more details.

-

- https://bitec-dsp.com/product/displayport-ip-core/?preview=true

- HDMI to DisplayPort demo on the EVD Kit using Bitec’s IP

- DP 1.4a functionality with up to 4-lane support

- Supports link of up to 2.7 Gbps line rate

- Up to 16-bit color support with RGB/ YCbCr formats

- DisplayPort receiver and transmitter boards

Lattice VIP DisplayPort Input module

|

|

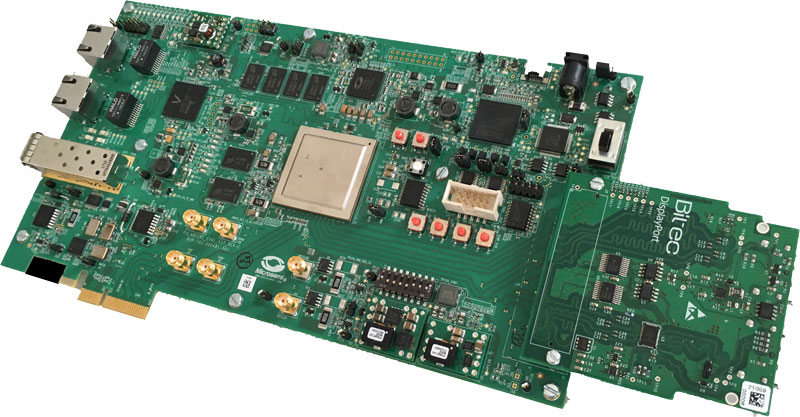

Microchip DisplayPort Evaluation Platform

A Microchip PolarFire Evaluation Platform is available upon request. The example design demonstrates a basic loop through at 8.1Gbps. The Example design supports MST and HDCP upon request.

- Full DP 1.4a functionality

- Link rates to 8.1Gbps

- Multistream Video Receiver and Transmitter

- 8K@30 loopthrough