Description

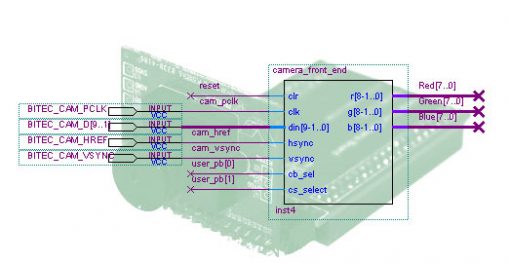

The Bitec Camera Front End IP allows developers to interface CMOS and CCD cameras to an Altera FPGA. Using a memory optimised line buffer, the core sits between a backend SoPC and the raw camera signals. As the line-buffer automatically adapts to the camera resolution, the back-end application can resize or window in real time. An optimised Bayer de-mosaic algorithm is then performed to produce an interpolated RGB triple. A gamma-correction layer allows the core to perform colour correction and user selectable colour space conversion. The core is designed to interface seamlessly to all CMOS and CCD devices.

Features

- Fully parameterised line buffer

- Auto line length adaptation for run-time resolution changes

- Minimal memory footprint

- Bayer to RGB conversion

- Colour bar output

- Gamma correction/Colour space conversion

IP Camera Front End