Description

Used in over 600 million devices, HDMI represents the most common interconnect standard for high definition video and audio.

The Bitec HDMI 2.1 IP Core enables HDMI inter-connectivity in FPGA or ASIC devices. Supporting uncompressed video formats to 8K60 4:2:0 and beyond, the Core is rich in parameterization to accomodatethe challenging timing closure requirements of FPGA to the power/size requirements of ASIC. The core also provides support for ARC/eARC and CEC 2.0.

Both Video and Audio is supported with added low-level access to Auxiliary data packets. This feature allows low level development and testing of HDMI interfaces. It also allows a more flexible interface to the latest 3D and 8K video formats and control packets.

The core provides convenient interfacing to 3rd party SERDES for rapid development of image processing systems. It is also designed to operate in parallel with the Bitec DP 1.4 IP Core to achieve DP++ compatibility.

Receiver Features

- HDMI 2.1 / 2.0b / 1.4a / DVI Compatible

- 8,10,12 & 16 bit Deep-color support

- 2- or 4-pixel per clock input/output

- 2-, 4- or 8-pixel per clock input/output

- Supports RGB, YCbCr Colorimetric Formats

- 2-, 8 and 32-channel Audio support

- 3D and MST Audio support

- Raw auxiliary data stream output

- Compatible with DVI and Dual-Link DVI Standards

- Optional CEC 1.4 and 2.0 support

- Optional HDCP 1.4/2.3 support

- Optional DSC 1.2a support

- Optional eARC support

Transmitter Features

- HDMI 2.1 / 2.0b / 1.4a / DVI Compatible

- 8,10,12 & 16 bit Deep-color support

- 2- or 4-pixel per clock input/output

- 2-, 4- or 8-pixel per clock input/output

- Supports RGB, YCbCr Colorimetric Formats

- 2-, 8 and 32-channel Audio support

- 3D and MST Audio support

- Raw auxiliary data stream output

- Compatible with DVI and Dual-Link DVI Standards

- Optional CEC 1.4 and 2.0 support

- Optional HDCP 1.4/2.3 support

- Optional DSC 1.2a support

- Optional eARC support

Technology Support : MicroSemi PolarFire, Lattice ECP5, Intel GX device, ASIC

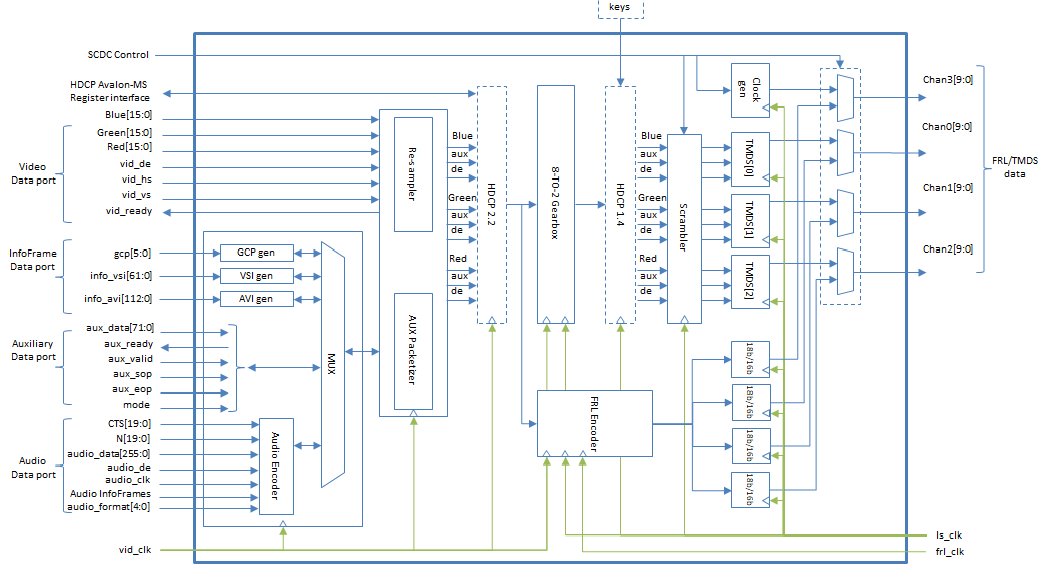

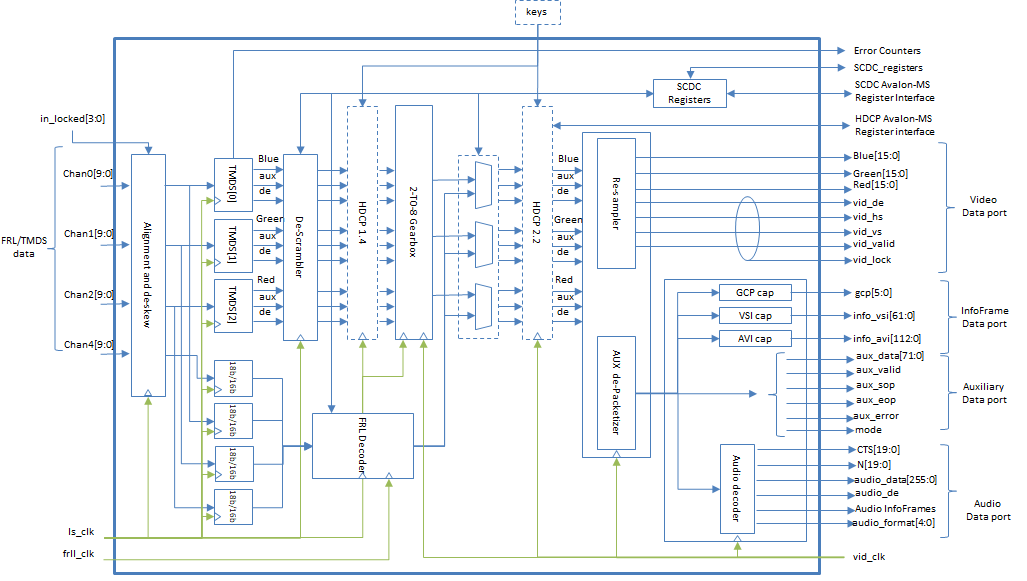

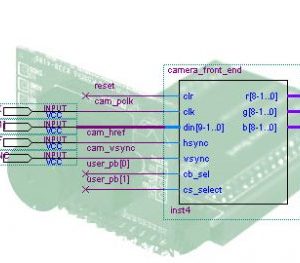

The HDMI core supports both sink and source with top level ports for Video, Audio and AUX packets. Additional AUX data paths allow for optional InfoFrame generation and/or 2/8/32-channel Audio.

Rich parameterization allows for balanced resource and Fmax allowing the IP to target low-cost/low-performance FPGAs to full ASIC applications. All aspects of the data paths are scalable including the PIXELS/clock, FRL CHARS/clock and TMDS SYMBOLS/clock.

Optional HDCP support allows HDCP 1.4/2.3 to be applied on the TMDS data path while HDCP 2.3 only is applied to the FRL data path. The HDCP 2.3 core can be parameterized to perform hardware based authentication or CPU based authentication.

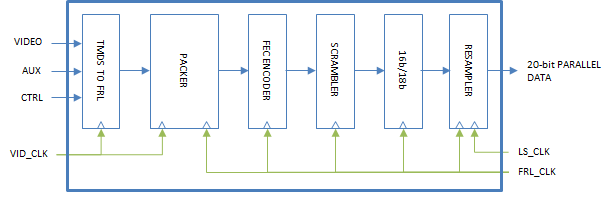

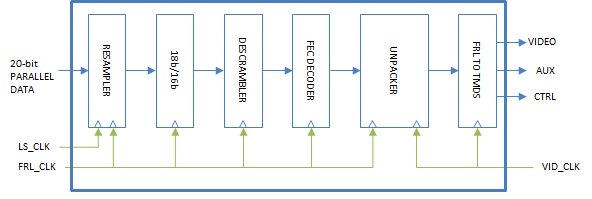

The FRL data paths for both source and sink can be parameterized to operate from 2- to 16-FRL CHARS /clk. They are designed for optimal resource usage while maintaining precise data-flow management.

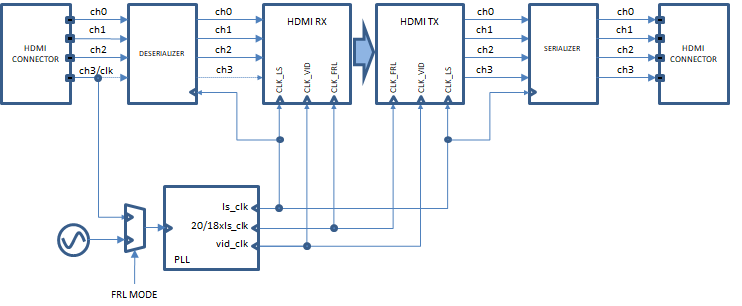

When running in FRL mode an additional FRL clock is required. The clock is responsible for constructing the FRL packet data according to the HDMI 2.1 Data Flow Monitoring requirements. The Fmax of this clock and be reduce by parameterizing the core FRL data path. Such parameterizations allow FRL mode to work in low-cost FPGA devices yet still achive optimal size/power for ASIC technologies. Independent data path clocking provides convenient power save features via clock-gating strategies.

When used in parallel with the Bitec DP 1.2 IP core, DP++ based designs are achieved.DP++ allows a single DP 1.2 interface connector to support both DP and HDMI connectivity.

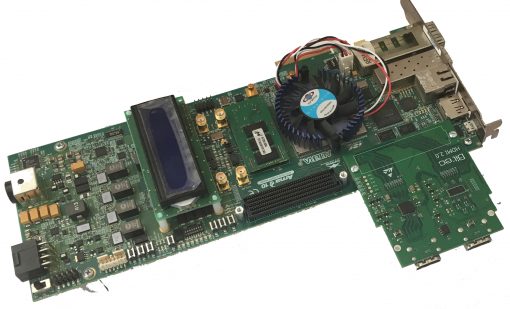

Intel Arria 10 FPGA Evaluation Platform

Evaluation platforms are available based on the FMC HDMI 2.1 Daughter Card. Reference designs are available which demonstrate the loop-through of video from source to sink on Intel Arria 10 FPGA development kits. Other device development kits are also supported. The example designs loop through source to sink up to 12Gbps with optional HDCP 1.4 and HDCP 2.2 support.

Optional DSC 1.2a

An optional DSC data path is available upon request. Added the DSC feature to HDMI 2.1 allows a much higher range of video formats. The DSC engine can be coupled to the Bitec DP 1.4a IP to ensure optimal designs by “sharing” the DSC core between DP and HDMI interfaces.