#### Product Brief:

# **HSMC Quad Video Daughter Card**

#### Features

- Four Separate Video Decoder Channels With following Features for Each Channel

- Accept NTSC (M, 4.43), PAL (B, D, G, H, I, M, N), and SECAM (B, D, G, K, K1, L)

- o Support ITU-R BT.601

- High-Speed 9-Bit ADC on each channel

- Two Composite Inputs or

One S-video Input (for Each Channel)

- o Brightness, Contrast, Saturation, Hue, and Sharpness Control Through i2c

- Four Independent Polymorphic Scalers

- Standard Programmable Video Input Format

- o ITU-R BT.656, 8-Bit 4:2:2 With Embedded Syncs

- o 8-Bit 4:2:2 With Discrete Syncs

- DVI Transmitter up to 165M pixels/second

- TV output supporting graphics resolutions up to 1024 x768 pixels

- Support for all NTSC and PAL formats on video output

- Provides CVBS, S-Video and SCART (RGB) outputs

## Applications

- Machine vision

- Video phone

- Remote image sensing

- Surveillance systems

- Biometrics

- Image recognition, filtering and compression

- Video streaming

### Compatibility

- HSMC interface specification compliant (Cyclone III and Stratix III kits)

- Compatible with all ALTERA and third party dev kits with HSMC interface

- Example software for Quartus II 7.1 and above

- Nois II examples provided

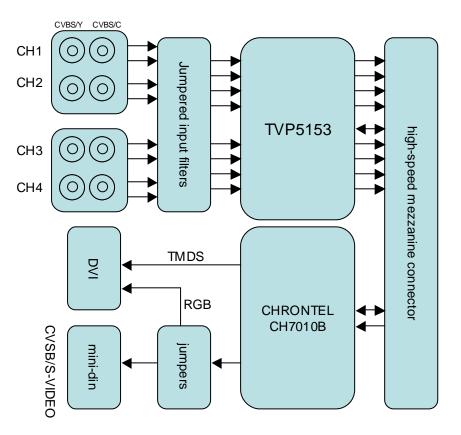

The hsmc quad video board is based on the Texas Instruments TVP5154 quad video

decoder. The analogue video inputs supported by the TVP5154 include composite video and Svideo. In general, the video decoder converts the analogue video input signal into digital component data. This data and the associated clocks from the video decoder are sent to the host fpga via the hsmc connector. A pre-scalar is integrated into the device which allows real-time scaling of input video data.

The device is controlled using i2c from the fpga.

Video output is based on the Chrontel CH7010B device. This device enables single-link DVI, component analogue and composite analogue video outputs. The device accepts digital, parallel video data and clocking from the host fpga via the hsmc connector. The host fpga is able to configure and monitor the device over an i2c link. A DVI output connector and mini-din output connector is present on the board.

For more information www.bitec-dsp.com

Altera, MegaCore and the Altera and Cyclone logos are Reg. U.S. Pat. & Tm. Off. and marks of Altera in and outside the US